# LMH0056 HD/SD SDI Reclocker with 4:1 Input Multiplexer

### **General Description**

The LMH0056 HD/SD SDI Reclocker with 4:1 Input Multiplexer retimes serial digital video data conforming to the SMPTE 292M and SMPTE 259M (A & C) standards. The LMH0056 operates at serial data rates of 143 Mbps, 270 Mbps, 1.483 Gbps and 1.485 Gbps. The LMH0056 supports DVB-ASI operation at 270 Mbps. The LMH0056 includes an integrated 4:1 input multiplexer for selecting one of four input data streams for retiming.

The LMH0056 automatically detects the incoming data rate and adjusts itself to retime the incoming data to suppress accumulated jitter. The LMH0056 recovers the serial data-rate clock and optionally provides it as an output. The LMH0056 has two differential serial data outputs; the second output may be selected as a low-jitter, data-rate clock output. Controls and indicators are: serial clock or second serial data output select, manual rate select input, SD/HD rate indicator output, lock detect output, auto/manual data bypass and output mute. The serial data inputs, outputs, and serial data-rate clock outputs are differential LVPECL compatible. The CML serial data and serial data-rate clock outputs are suitable for driving  $100\Omega$  differentially terminated networks. The control logic inputs and outputs are LVCMOS compatible.

The LMH0056 is powered from a single 3.3V supply. Power dissipation is typically 360 mW. The device is housed in a 48-pin LLP package.

#### **Features**

- Supports SMPTE 292M and SMPTE 259M (A & C) serial digital video standards

- Supports 143 Mbps, 270 Mbps, 1.483 Gbps, and 1.485 Gbps serial data rate operation

- Supports DVB-ASI at 270 Mbps

- Single 3.3V supply operation

- 360 mW typical power consumption

- Integrated 4:1 multiplexed input

- Two differential, reclocked outputs

- Choice of second reclocked output or low-jitter, differential, data-rate clock output

- Single 27 MHz external crystal or reference clock input

- Manual rate select input

- SD/HD operating rate indicator output

- Lock Detect indicator output

- Output mute function for data and clock

- Auto/Manual reclocker bypass

- Differential LVPECL compatible serial data inputs and outputs

- LVCMOS control inputs and indicator outputs

- 48-Pin LLP package

- Industrial temperature range: -40°C to +85°C

## **Applications**

- SDTV/HDTV serial digital video interfaces for:

- Digital video routers and switchers

- Digital video processing and editing equipment

- DVB-ASI equipment

- Video standards and format converters

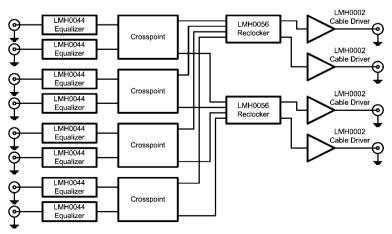

# **Typical Application**

20201901

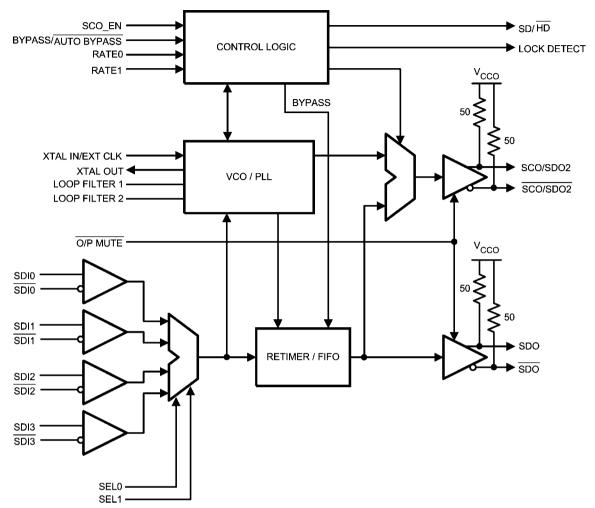

# **Block Diagram**

20201903

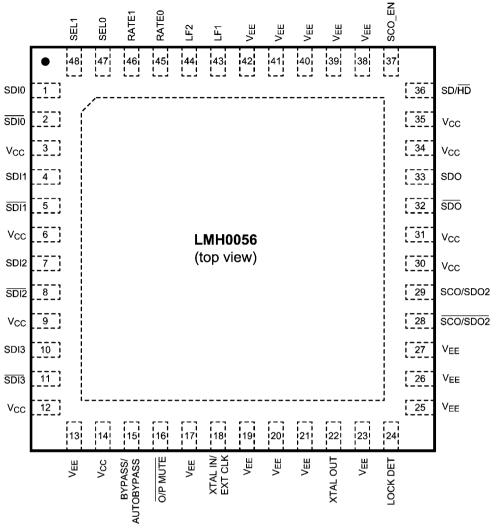

## **Connection Diagram**

20201902

The exposed die attach pad is the primary negative electrical terminal for this device. It must be connected to the negative power supply voltage.

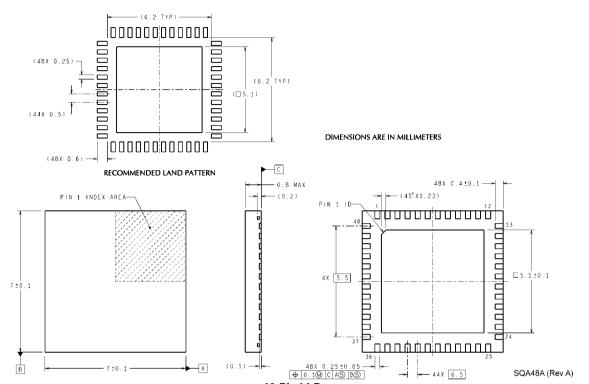

48-Pin LLP Order Number LMH0056SQ See NS Package Number SQA48A

# **Pin Descriptions**

| Pin | Name               | Description                                                                           |  |  |

|-----|--------------------|---------------------------------------------------------------------------------------|--|--|

| 1   | SDI0               | Data Input 0 True                                                                     |  |  |

| 2   | SDI0               | Data Input 0 Complement                                                               |  |  |

| 3   | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 4   | SDI1               | Data Input 1 True                                                                     |  |  |

| 5   | SDI1               | Data Input 1 Complement                                                               |  |  |

| 6   | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 7   | SDI2               | Data Input 2 True                                                                     |  |  |

| 8   | SDI2               | Data Input 2 Complement                                                               |  |  |

| 9   | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 10  | SDI3               | Data Input 3 True                                                                     |  |  |

| 11  | SDI3               | Data Input 3 Complement                                                               |  |  |

| 12  | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 13  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 14  | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 15  | BYPASS/AUTO BYPASS | Bypass/Auto Bypass mode select                                                        |  |  |

| 16  | OUTPUT MUTE        | Data and Clock Output Mute input (active low)                                         |  |  |

| 17  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 18  | XTAL IN/EXT CLK    | Crystal or External Oscillator input                                                  |  |  |

| 19  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 20  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 21  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 22  | XTAL OUT           | Crystal Oscillator output                                                             |  |  |

| 23  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 24  | LOCK DETECT        | PLL Lock Detect output (active high)                                                  |  |  |

| 25  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 26  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 27  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 28  | SCO/SDO2           | Serial Clock or Serial Data Output 2 Complement                                       |  |  |

| 29  | SCO/SDO2           | Serial Clock or Serial Data Output 2 True                                             |  |  |

| 30  | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 31  | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 32  | SDO                | Data Output Complement                                                                |  |  |

| 33  | SDO                | Data Output True                                                                      |  |  |

| 34  | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 35  | V <sub>CC</sub>    | Positive power supply input                                                           |  |  |

| 36  | SD/HD              | Data Rate Range output                                                                |  |  |

| 37  | SCO_EN             | Serial Clock or Serial Data 2 Output select (active high enables serial clock output) |  |  |

| 38  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 39  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 40  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 41  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 42  | V <sub>EE</sub>    | Negative power supply input                                                           |  |  |

| 43  | LF1                | Loop Filter                                                                           |  |  |

| 44  | LF2                | Loop Filter                                                                           |  |  |

| 45  | RATE 0             | Data Rate select input                                                                |  |  |

| 46  | RATE 1             | Data Rate select input                                                                |  |  |

|     | SEL0               | Data Input select input                                                               |  |  |

| Pin | Name | Description                                           |

|-----|------|-------------------------------------------------------|

| 48  | SEL1 | Data Input select input                               |

| DAP | Vee  | Connect exposed DAP to negative power supply (ground) |

## **Absolute Maximum Ratings** (Note 1)

It is anticipated that this device will not be offered in a military qualified version. If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>–V<sub>EE</sub>) 4.0V Logic Supply Voltage (Vi)  $V_{EE}-0.15V \text{ to } V_{CC} \\ +0.15V$

Logic Input Current (single input):

Serial Data Input Voltage ( $V_{SDI}$ )  $V_{CC}$  to  $V_{CC}$ –2.0V Serial Data Output Sink Current ( $I_{SDO}$ ) 24 mA

Package Thermal Resistance

$\theta_{JA}$  48-pin LLP 26.1°C/W  $\theta_{JC}$  48-pin LLP 1.9°C/W

Storage Temp. Range -65°C to +150°C

Junction Temperature +150°C

Lead Temperature (Soldering 4 Sec) +260°C (Pb-free)

ESD Rating (HBM) 8 kV

ESD Rating (MM) 400V

ESD Rating (CDM) 1250V

# Recommended Operating Conditions

Supply Voltage ( $V_{CC}$ – $V_{EE}$ ) 3.3V ±5% Logic Input Voltage  $V_{EE}$  to  $V_{CC}$ Differential Serial Input Voltage 800 mV ±10%

Serial Data or Clock Output Sink

Current ( $I_{SO}$ ) 16 mA max. Operating Free Air Temperature ( $T_A$ ) -40°C to +85°C

### **DC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified. (Notes 2, 3)

| Symbol            | Parameter                                   | Conditions                        | Reference     | Min                  | Тур                                    | Max                   | Units             |

|-------------------|---------------------------------------------|-----------------------------------|---------------|----------------------|----------------------------------------|-----------------------|-------------------|

| V <sub>IH</sub>   | Input Voltage High Level                    |                                   | Logic inputs  | 2                    |                                        | V <sub>CC</sub>       | V                 |

| V <sub>IL</sub>   | Input Voltage Low Level                     |                                   |               | V <sub>EE</sub>      |                                        | 0.8                   | V                 |

| I <sub>IH</sub>   | Input Current High Level                    | $V_{IH} = V_{CC}$                 |               |                      | 1                                      | 65                    | μA                |

| I <sub>IL</sub>   | Input Current Low Level                     | $V_{IL} = V_{EE}$                 |               |                      | -1                                     | -25                   | μA                |

| V <sub>OH</sub>   | Output Voltage High Level                   | I <sub>OH</sub> = -2 mA           | Logic outputs | 2                    |                                        |                       | V                 |

| V <sub>OL</sub>   | Output Voltage Low Level                    | I <sub>OL</sub> = +2 mA           |               |                      |                                        | V <sub>EE</sub> + 0.6 | V                 |

| V <sub>SDID</sub> | Serial Input Voltage,<br>Differential       |                                   | SDI           | 200                  |                                        | 1600                  | mV <sub>P-P</sub> |

| V <sub>CMI</sub>  | Input Common Mode<br>Voltage                |                                   |               | V <sub>CC</sub> -1.6 |                                        | V <sub>CC</sub> -0.2  | V                 |

| V <sub>SDOD</sub> | Serial Output Voltage,<br>Differential      | $100\Omega$ differential load     | SDO, SCO      | 720                  | 800                                    | 880                   | mV <sub>P-P</sub> |

| V <sub>CMO</sub>  | Output Common Mode<br>Voltage               | $100\Omega$ differential load     |               |                      | V <sub>CC</sub> -<br>V <sub>SDOD</sub> |                       | V                 |

| I <sub>cc</sub>   | Power Supply Current,<br>3.3V supply, Total | 1485 Mbps, NTSC color bar pattern |               |                      | 109                                    |                       | mA                |

## **AC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified. (Note 3)

| Symbol                          | Parameter                                                   | Conditions                             | Reference     | Min  | Тур           | Max  | Units             |

|---------------------------------|-------------------------------------------------------------|----------------------------------------|---------------|------|---------------|------|-------------------|

| BR <sub>SD</sub>                | Serial Data Rate                                            | SMPTE 259M, A                          | SDI, SDO      |      | 143           |      | Mbps              |

| BR <sub>SD</sub>                | Serial Data Rate                                            | SMPTE 259M, C                          | ]             |      | 270           |      | Mbps              |

| BR <sub>SD</sub>                | Serial Data Rate                                            | SMPTE 292M                             |               |      | 1483,<br>1485 |      | Mbps              |

| TOL <sub>JIT</sub>              | Serial Input Jitter<br>Tolerance                            | 143 or 270 Mbps,<br>(Notes 7, 9, 12)   | SDI           |      | >6            |      | UI <sub>P-P</sub> |

| TOL <sub>JIT</sub>              | Serial Input Jitter<br>Tolerance                            | 143 or 270 Mbps,<br>(Notes 7, 8, 10)   |               | >0.6 |               |      | UI <sub>P-P</sub> |

| TOL <sub>JIT</sub>              | Serial Input Jitter<br>Tolerance                            | 1483 or 1485 Mbps,<br>(Notes 7, 8, 9)  |               | >6   |               |      | UI <sub>P-P</sub> |

| TOL <sub>JIT</sub>              | Serial Input Jitter<br>Tolerance                            | 1483 or 1485 Mbps,<br>(Notes 7, 8, 10) |               | >0.6 |               |      | UI <sub>P-P</sub> |

| t <sub>JIT</sub>                | Serial Data Output Jitter                                   | 143 Mbps, (Notes 8, 11)                | SDO           |      | 0.02          | 0.08 | UI <sub>P-P</sub> |

| t <sub>JIT</sub>                | Serial Data Output Jitter                                   | 270 Mbps, (Notes 8, 11)                | 1             |      | 0.02          | 0.08 | UI <sub>P-P</sub> |

| t <sub>JIT</sub>                | Serial Data Output Jitter                                   | 1483 or 1485 Mbps,<br>(Notes 8, 11)    |               |      | 0.05          | 0.1  | UI <sub>P-P</sub> |

| BW <sub>LOOP</sub>              | Loop Bandwidth                                              | 270 Mbps,<br><0.1dB Peaking            |               |      | 300           |      | kHz               |

|                                 |                                                             | 1485 Mbps,<br><0.1dB Peaking           |               |      | 2.0           |      | MHz               |

| F <sub>CO</sub>                 | Serial Clock Output<br>Frequency                            | 143 Mbps data rate                     | SCO           |      | 143           |      | MHz               |

| F <sub>CO</sub>                 | Serial Clock Output<br>Frequency                            | 270 Mbps data rate                     | _             |      | 270           |      | MHz               |

| F <sub>CO</sub>                 | Serial Clock Output<br>Frequency                            | 1483 Mbps data rate                    |               |      | 1483          |      | MHz               |

| F <sub>CO</sub>                 | Serial Clock Output<br>Frequency                            | 1485 Mbps data rate                    |               |      | 1485          |      | MHz               |

| t <sub>JIT</sub>                | Serial Clock Output Jitter                                  |                                        | ]             |      | 2             | 3    | ps <sub>RMS</sub> |

|                                 | Serial Clock Output Alignment with respect to Data Interval |                                        | SDO, SCO      | 40   |               | 60   | %                 |

|                                 | Serial Clock Output Duty<br>Cycle                           |                                        | sco           | 45   |               | 55   | %                 |

| T <sub>ACQ</sub>                | Acquisition Time                                            | Auto-Rate Detect Mode,<br>(Notes 4, 6) |               |      | 10            | 16   | ms                |

|                                 |                                                             | Fixed Rate Mode,<br>(Notes 4, 6)       |               |      | 1             | 6    | ms                |

| t <sub>r</sub> , t <sub>f</sub> | Input rise/fall time                                        | 10%–90%                                | Logic inputs  |      | 1.5           | 3    | ns                |

| t <sub>r</sub> , t <sub>f</sub> | Input rise/fall time                                        | 20%–80%, 143 or 270<br>Mbps            | SDI           |      |               | 1500 | ps                |

| t <sub>r</sub> , t <sub>f</sub> | Input rise/fall time                                        | 20%–80%, 1483 or 1485<br>Mbps          |               |      |               | 270  | ps                |

| t <sub>r</sub> , t <sub>f</sub> | Output rise/fall time                                       | 10%–90%                                | Logic outputs |      | 1.5           | 3    | ns                |

| t <sub>r</sub> , t <sub>f</sub> | Output rise/fall time                                       | 20%-80%, (Note 5)                      | SDO, SCO      |      | 90            | 130  | ps                |

| F <sub>REF</sub>                | Reference Clock<br>Frequency                                |                                        |               |      | 27            |      | MHz               |

| F <sub>TOL</sub>                | Reference Clock<br>Frequency Tolerance                      |                                        |               |      | ±50           |      | ppm               |

**Note 1:** "Absolute Maximum Ratings" are those parameter values beyond which the life and operation of the device cannot be guaranteed. The stating herein of these maximums shall not be construed to imply that the device can or should be operated at or beyond these values. The table of "Electrical Characteristics" specifies acceptable device operating conditions.

Note 2: Current flow into device pins is defined as positive. Current flow out of device pins is defined as negative. All voltages are referenced to V<sub>EE</sub> (equal to zero volts).

Note 3: Typical values are stated for:  $V_{CC}$  = +3.3V,  $T_A$  = +25°C.

Note 4: Spec is guaranteed by design.

**Note 5:**  $R_L = 100\Omega$  differential.

Note 6: Measured from first SDI transition until Lock Detect (LD) output goes high (true).

Note 7: Peak-to-peak amplitude with sinusoidal modulation per SMPTE RP 184-1996 paragraph 4.1. The test data signal shall be color bars.

Note 8: This parameter is guaranteed by characterization over voltage and temperature limits.

Note 9: Refer to "A1" in Figure 1 of SMPTE RP 184-1996.

Note 10: Refer to "A2" in Figure 1 of SMPTE RP 184-1996.

Note 11: Serial Data Output Jitter is total output jitter with 0.2UI<sub>P-P</sub> input jitter.

Note 12: Characterized to the limitations of SDI test equipment.

### **Device Description**

The LMH0056 HD/SD SDI Reclocker with 4:1 Input Multiplexer is used in many types of digital video signal processing equipment. Supported serial digital video standards are SMPTE 259M (A & C) and SMPTE 292M. Corresponding serial data rates are 143 Mbps, 270 Mbps, 1,483 Gbps and 1.485 Gbps. DVB-ASI data at 270 Mbps may also be retimed. The LMH0056 retimes the serial data stream to suppress accumulated jitter. It provides two low-jitter, differential, serial data outputs. The second output may be selected to output either serial data or a low-iitter serial data-rate clock. Controls and indicators are: serial data-rate clock or second serial data output select, manual rate select input, SD/HD rate output, lock detect output, auto/manual data bypass and output mute. Serial data inputs are CML and LVPECL compatible. Serial data and data-rate clock outputs are differential CML and produce LVPECL compatible levels. The output buffer design can drive AC or DC-coupled, terminated 100Ω differential loads. The differential output level is 800 mV<sub>P-P</sub> ±10% into  $100\Omega$  AC or DC-coupled differential loads. Logic inputs and outputs are LVCMOS compatible.

The device package is a 48–pin LLP with an exposed die attach pad. The exposed die attach pad is electrically connected to device ground ( $V_{\rm EE}$ ) and is the primary negative electrical terminal for the device. This terminal must be connected to the negative power supply or circuit ground.

# Serial Data Inputs, Serial Data and Clock Outputs

#### **SERIAL DATA INPUT AND OUTPUTS**

The differential serial data inputs, SDI0-SDI3, accept serial digital video data at the rates specified in *Table 1*. The serial

data inputs are differential LVPECL compatible. These inputs are intended to be DC interfaced to devices such as the LMH0034 adaptive cable equalizer. These inputs are not internally terminated or biased. The inputs may be AC-coupled if a suitable input bias voltage is provided.

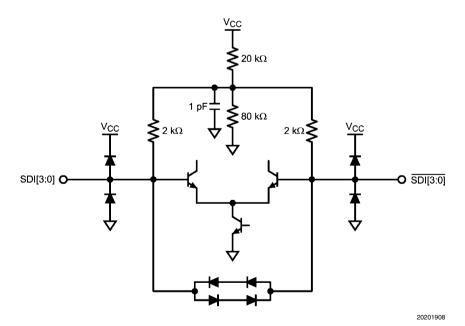

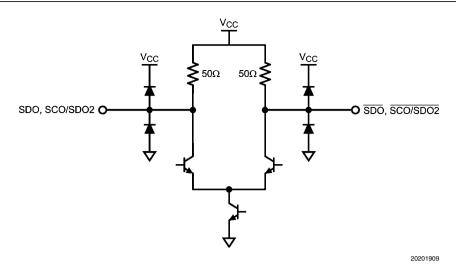

The LMH0056 provides four independent, multiplexed data inputs. The active input channel is selected via the SEL0 and SEL1 pins, as shown in *Table 2. Figure 1* shows the equivalent input circuit for SDI[3:0] and SDI[3:0].

The LMH0056 has two, retimed, differential, serial data outputs, SDO and SCO/SDO2. These outputs provide low jitter, differential, retimed data to devices such as the LMH0002 cable driver or the LMH0031 deserializer. Output SCO/SDO2 is multiplexed and can provide either a second serial data output or a serial data-rate clock output. *Figure 2* shows the equivalent output circuit for SDO, SDO, SCO/SDO2, and SCO/SDO2.

The SCO\_EN input controls the operating mode for the SCO/SDO2 output. When the SCO\_EN input is high the SCO/SDO2 output provides a serial data-rate clock. When SCO\_EN is low, the SCO/SDO2 output provides retimed serial data.

Both differential serial data outputs, SDO and SCO/SDO2, are muted when the  $\overline{\text{MUTE}}$  input is a logic low level. SCO/SDO2 also mutes when the Bypass mode is activated when this output is operating as the serial clock output. When muted, SDO and  $\overline{\text{SDO}}$  (or SDO2 and  $\overline{\text{SDO2}}$ ) will assume opposite differential output levels. The CML serial data outputs are differential LVPECL compatible. These outputs have internal 50 $\Omega$  pull-ups and are suitable for driving AC or DC-coupled, 100 $\Omega$  center-tapped, AC grounded or 100 $\Omega$  un-center-tapped, differentially terminated networks.

FIGURE 1. Equivalent SDI Input Circuit (SDI[3:0], SDI[3:0])

FIGURE 2. Equivalent SDO Output Circuit (SDO, SDO, SCO/SDO2, SCO/SDO2)

#### **OPERATING SERIAL DATA RATES**

This device operates at serial data rates of 143 Mbps, 270 Mbps, 1483 Mbps and 1485 Mbps. The device does not lock to harmonics of these rates. The device does not lock and automatically enters the reclocker bypass mode for the following data rates: 177 Mbps, 360 Mbps, and 540 Mbps.

#### SERIAL DATA CLOCK/SERIAL DATA 2 OUTPUT

The Serial Data Clock/Serial Data 2 Output is controlled by the SCO\_EN input and provides either a second retimed serial data output or a low jitter differential clock output appropriate to the serial data rate being processed. When operating as a serial clock output, the rising edge of the clock will be positioned within the corresponding serial data bit interval within 10% of the center of the data interval.

Differential output SCO/SDO2 functions as the second serial data output when the SCO\_EN input is a logic-low level. This output functions as the serial data-rate clock output when the SCO\_EN input is a logic-high level. The SCO\_EN input has an internal pull-down device and the default state of SCO\_EN is low (serial data output 2 enabled). SCO/SDO2 is muted when the MUTE input is a logic low level. When the Bypass mode is activated and this output is functioning as a serial clock output, the output will also be muted.

# Control Inputs and Indicator Outputs

#### **SERIAL DATA RATE SELECTOR**

The Serial Data Rate Selector (RATE [1:0]) permits the user to fix the operating serial data rate. The pins have internal pull-

downs which maintain a logic-low input condition unless externally driven to a logic-high condition. This input also serves to place the device in a test mode. The codes shown in *Table 1* select the desired operating serial data rate. The LMH0056 then enters either the Auto-Rate Detect mode or a single operating rate. Selecting the 270 Mbps rate mode may also be used when reclocking DVB-ASI data. DVB-ASI data is MPEG2 coded data that is transmitted in 8B10B coding. The device will reclock this data without harmonic locking.

**TABLE 1. Data Rate Select Input Codes**

| RATE [1:0]<br>Code | Data Rate or Mode | Comments                    |

|--------------------|-------------------|-----------------------------|

| 00                 | Auto-Rate         | 143 Mbps rate operation     |

|                    | Detect            | supported only in ARD mode  |

|                    | mode              |                             |

| 01                 | 270 Mbps          | May be used to support DVB- |

|                    |                   | ASI operation               |

| 10                 | 1483/1485         |                             |

|                    | Mbps              |                             |

#### SERIAL DATA INPUT SELECTOR

The Serial Data Input Selector (SEL [1:0]) allows the user to select the active input channel. *Table 2* shows the input selected for a given state of SEL [1:0].

**TABLE 2. Data Input Select Codes**

| SEL [1:0] Code | Selected Input |

|----------------|----------------|

| 00             | SDI0           |

| 01             | SDI1           |

| 10             | SDI2           |

| 11             | SDI3           |

#### **LOCK DETECT**

The Lock Detect (LD) output, when high, indicates that data is being received and the PLL is locked. LD may be connected to the MUTE input to mute the data and clock outputs when no data signal is being received. See *Table 3*.

#### MUTE

The MUTE input, when low, mutes the serial data and clock outputs. It may be connected to Lock Detect or externally driven to mute or un-mute the outputs. If MUTE is connected to LD, then the data and clock outputs are muted when the PLL is not locked. This function overrides the Bypass function: see *Table 3*. MUTE has an internal pull-up device to enable the output by default.

#### **BYPASS/AUTO BYPASS**

The Bypass/Auto Bypass input, when high, forces the device to output the data without reclocking it. When this input is low, the device automatically bypasses the reclocking function when the device is in an unlocked condition or the detected data rate is a rate which the device does not support. See *Table 3*. BYPASS/AUTO BYPASS has an internal pull-down device.

**TABLE 3. Control Functionality**

| LOCK DETECT | LOCK DETECT   OUTPUT MUTE   BYPASS/AUTO BYPASS   DEVICE |   | DEVICE STATUS                                             |

|-------------|---------------------------------------------------------|---|-----------------------------------------------------------|

| 0           | 1                                                       | 0 | PLL unlocked, reclocker bypassed                          |

| 1           | 1                                                       | 0 | PLL locked to supported data rate, reclocker not bypassed |

| X           | 0                                                       | Χ | Outputs muted                                             |

| 0           | LOCK DETECT                                             | X | Outputs muted                                             |

| 1           | LOCK DETECT                                             | 0 | PLL locked to supported data rate, reclocker not bypassed |

| 1           | LOCK DETECT                                             | 1 | PLL locked to supported data rate, reclocker bypassed     |

| X           | 1                                                       | 1 | Outputs not muted, reclocker bypassed                     |

#### SD/HD

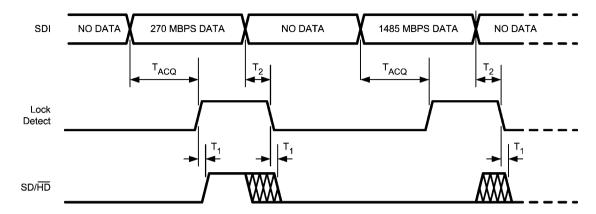

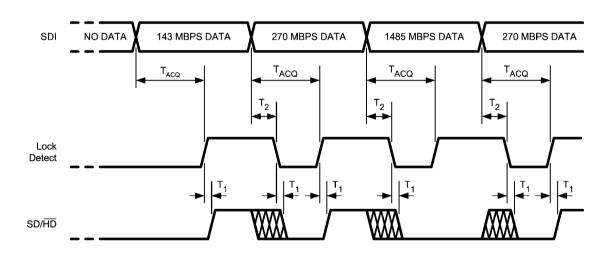

The SD/HD output indicates whether the LMH0056 is processing SD or HD data rates. It may be used to control another device such as the LMH0002 cable driver. When this output is high it indicates that the data rate is 270 Mbps (or 143 Mbps). When low, the indicated data rate is 1483 or 1485 Mbps. The SD/HD output is a registered function and is

only valid when the PLL is locked and the Lock Detect output is high. When the PLL is not locked (the Lock Detect output is low), the SD/HD output defaults to HD (low). The SD/HD output is undefined for a short time after lock detect assertion or de-assertion due to a data rate change on SDI. See *Figure 3* for a timing diagram showing the relationship between SDI, Lock Detect, and SD/HD.

T<sub>ACO</sub> = Acquisition Time, defined in the AC Electrical Characteristics Table

$T_1$  = Time from Lock Detect assertion or deassertion until SD/ $\overline{\text{HD}}$  output is valid, typically 37 ns (one 27 MHz clock period)

$T_2$  = Time from SDI input change until Lock Detect de-assertion, 1 ms maximum. SD/ $\overline{\text{HD}}$  output is not valid during this time.

20201905

FIGURE 3. SDI, Lock Detect, and SD/HD

#### SCO\_EN

Input SCO\_EN enables the SCO/SDO2 differential output to function either as a serial data-rate clock or second serial data output. SCO/SDO2 functions as a serial data-rate clock when SCO\_EN is high. This pin has an internal pull-down device. The default state (low) enables the SCO/SDO2 output as a second serial data output.

#### **CRYSTAL OR EXTERNAL CLOCK REFERENCE**

The LMH0056 uses a 27 MHz crystal or external clock signal as a timing reference input. A 27 MHz parallel resonant crystal and load network may be connected to the XTAL IN/EXT CLK and XTAL OUT pins. Alternatively, a 27 MHz LVCMOS compatible clock signal may be input to XTAL IN/EXT CLK. Parameters for a suitable crystal are given in *Table 4*.

**TABLE 4. Crystal Parameters**

| Parameter           | Value                             |

|---------------------|-----------------------------------|

| Frequency           | 27 MHz                            |

| Frequency Stability | ±50 ppm @ recommended drive level |

| Parameter               | Value                      |

|-------------------------|----------------------------|

| Operating Mode          | Fundamental mode, Parallel |

|                         | Resonant                   |

| Load Capacitance        | 20 pF                      |

| Shunt Capacitance       | 7 pF                       |

| Series Resistance       | 40Ω max.                   |

| Recommended Drive Level | 100 μW                     |

| Maximum Drive Level     | 500 μW                     |

| Operating Temperature   | -10°C to +60°C             |

| Range                   |                            |

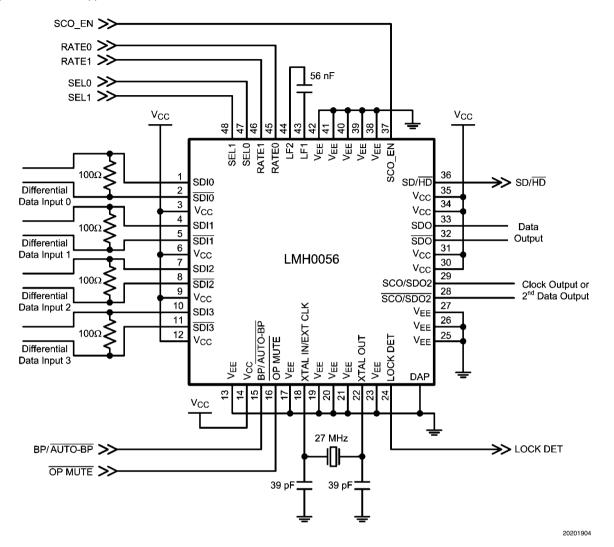

## **Application Information**

Figure 4 shows an application circuit for the LMH0056.

**FIGURE 4. Application Circuit**

## Physical Dimensions inches (millimeters) unless otherwise noted

48-Pin LLP Order Number LMH0056SQ NS Package Number SQA48A

### **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright@ 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560